|                        |           |                |                       | REVISIONS |       |       |     |      |                                                                                      |     |             |      |      |        |         |        |                |       |          |  |

|------------------------|-----------|----------------|-----------------------|-----------|-------|-------|-----|------|--------------------------------------------------------------------------------------|-----|-------------|------|------|--------|---------|--------|----------------|-------|----------|--|

|                        |           |                | L                     | ΓR        |       |       |     | DESC | RIPTI                                                                                | ON  |             |      |      | D      | ATE     |        | ļ              | APPR  | OVED     |  |

|                        |           |                |                       |           |       |       |     |      |                                                                                      |     |             |      |      |        |         |        |                |       |          |  |

|                        |           |                |                       |           |       |       |     |      |                                                                                      |     |             |      |      |        |         |        |                |       |          |  |

|                        |           |                |                       |           |       |       |     |      |                                                                                      |     |             |      |      |        |         |        |                |       |          |  |

|                        |           |                |                       |           |       |       |     |      |                                                                                      |     |             |      |      |        |         |        |                |       |          |  |

|                        |           |                |                       |           |       |       |     |      |                                                                                      |     |             |      |      |        |         |        |                |       |          |  |

|                        |           |                |                       |           |       |       |     |      |                                                                                      |     |             |      |      |        |         |        |                |       |          |  |

|                        |           |                |                       |           |       |       |     |      |                                                                                      |     |             |      |      |        |         |        |                |       |          |  |

|                        |           |                |                       |           |       |       |     |      |                                                                                      |     |             |      |      |        |         |        |                |       |          |  |

|                        |           |                |                       |           |       |       |     |      |                                                                                      |     |             |      |      |        |         |        |                |       |          |  |

|                        |           |                |                       |           |       |       |     |      |                                                                                      |     |             |      |      |        |         |        |                |       |          |  |

|                        |           |                |                       |           |       |       |     |      |                                                                                      |     |             |      |      |        |         |        |                |       |          |  |

|                        |           |                |                       |           |       |       |     |      |                                                                                      |     |             |      |      |        |         |        |                |       |          |  |

|                        |           |                |                       |           |       |       |     |      |                                                                                      |     |             |      |      |        |         |        |                |       |          |  |

|                        |           |                |                       |           |       |       |     |      |                                                                                      |     |             |      |      |        |         |        |                |       |          |  |

|                        |           |                |                       |           |       |       |     |      |                                                                                      |     |             |      |      |        |         |        |                |       |          |  |

|                        |           |                |                       |           |       |       |     |      |                                                                                      |     |             |      |      |        |         |        |                |       |          |  |

|                        |           |                |                       |           |       |       |     |      |                                                                                      |     |             |      |      |        |         |        |                |       |          |  |

|                        |           |                |                       |           |       |       |     |      |                                                                                      |     |             |      |      |        |         |        |                |       |          |  |

|                        |           |                |                       |           |       |       |     |      |                                                                                      |     |             |      |      |        |         |        |                |       |          |  |

| Prepared in ac         | cordance  | e with AS      | ME Y1                 | 4.24      |       |       |     |      |                                                                                      |     |             |      |      |        |         | Ve     | ndor it        | em dr | awing    |  |

| REV                    |           |                |                       |           |       |       |     |      |                                                                                      |     |             |      |      |        |         |        |                |       |          |  |

| PAGE                   |           |                |                       |           |       |       |     |      |                                                                                      |     |             |      |      |        |         |        |                |       |          |  |

| REV                    |           |                |                       |           |       |       |     |      |                                                                                      |     |             |      |      |        |         |        |                |       |          |  |

| PAGE                   |           |                |                       |           |       |       |     |      |                                                                                      |     |             |      |      |        |         |        |                |       | 1        |  |

| REV STATUS             | <u> </u>  | REV            | 1                     |           |       |       |     |      |                                                                                      |     |             |      |      |        |         |        |                |       | 1        |  |

| OF PAGES               | Ī         | PAGE           |                       | 1         | 2     | 3     | 4   | 5    | 6                                                                                    | 7   | 8           | 9    | 10   | 11     | 12      | 13     | 14             |       |          |  |

| PMIC N/A               | l         |                | <b>EPARI</b><br>CK OF |           |       | •     |     | •    | •                                                                                    |     |             |      |      |        |         |        | RITIN<br>218-3 |       | •        |  |

| Original date of YY-MM | f drawing | CH<br>R/       | <b>ECKEI</b><br>AJESH |           | ADIA  |       |     |      |                                                                                      | TIT |             | NDO: | UT 1 | יי ביי | - A I ' | 1N1= 4 | \D 4           | 0 017 | <b>-</b> |  |

|                        |           | PROVI<br>HARLE |                       |           | E     |       |     |      | MICROCIRCUIT, DIGITAL-LINEAR, 12-BIT ANALOG TO DIGITAL CONVERTER, MONOLITHIC SILICON |     |             |      |      |        |         |        |                |       |          |  |

|                        |           | S              | IZE                   | COD       | E IDE | NT. N | О.  |      | DWG NO.                                                                              |     |             |      |      |        |         |        |                |       |          |  |

|                        |           |                | Α                     |           |       | 162   | 236 |      |                                                                                      |     |             |      | 1    | /62    | /11     | 61     | 1              |       |          |  |

|                        |           | RE             | V                     | <u>I</u>  |       |       |     |      |                                                                                      | PAG | <b>SE</b> 1 | OF   | 14   |        |         |        |                |       |          |  |

AMSC N/A 5962-V056-11

#### 1. SCOPE

- 1.1 <u>Scope</u>. This drawing documents the general requirements of a high performance 12 bit analog to digital converter microcircuit, with an operating temperature range of -55°C to +125°C.

- 1.2 <u>Vendor Item Drawing Administrative Control Number</u>. The manufacturers PIN is the item of identification. The vendor item drawing establishes an administrative control number for identifying the item on the engineering documentation:

V62/11611

01

X

E

Drawing number

Device type (See 1.2.1)

Case outline (See 1.2.2)

Lead finish (See 1.2.3)

1.2.1 Device type(s).

Device typeGenericCircuit function01AD7476-EP12 bit analog to digital converter

1.2.2 <u>Case outline(s)</u>. The case outline(s) are as specified herein.

Outline letter

Number of pins

JEDEC PUB 95

Package style

X

6

MO-178-AB

Plastic small outline surface mount

1.2.3 <u>Lead finishes</u>. The lead finishes are as specified below or other lead finishes as provided by the device manufacture:

Finish designator

A Hot solder dip

B Tin-lead plate

C Gold plate

D Palladium

E Gold flash palladium

Z Other

| DLA LAND AND MARITIME |  | CODE IDENT NO. | DWG NO.          |

|-----------------------|--|----------------|------------------|

| COLUMBUS, OHIO        |  | <b>16236</b>   | <b>V62/11611</b> |

|                       |  | REV            | PAGE 2           |

## 1.3 Absolute maximum ratings. 1/

|     | Supply voltage (V <sub>DD</sub> ) to ground (GND)  Analog input voltage to GND  Digital input voltage to GND  Digital output voltage to GND  Input current to any pin except supplies                                                                                                               | -0.3 V to V <sub>DD</sub> + 0.3 V<br>-0.3 V to 7 V<br>-0.3 V to V <sub>DD</sub> + 0.3 V<br>$\pm 10$ m A $\underline{2}/$ |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------|

|     | Junction temperature range (T <sub>J</sub> )  Storage temperature range (T <sub>STG</sub> )  Lead temperature, soldering reflow (10 seconds to 30 seconds)  Lead (Pb) free temperature, soldering reflow  Electrostatic discharge (ESD)  Thermal resistance, junction to ambient (θ <sub>JC</sub> ) | -65°C to +150°C<br>235°C<br>255°C<br>3.5 kV                                                                              |

| 1.4 | Thermal resistance, junction to ambient (θ <sub>JA</sub> )  Recommended operating conditions. 3/ 4/  Supply voltage (V <sub>DD</sub> ) range                                                                                                                                                        | +2.35 V to +5.25 V                                                                                                       |

<sup>4/</sup> All ratings and specifications, please refer to the relevant EP datasheet.

| DLA LAND AND MARITIME |  | CODE IDENT NO. | DWG NO.          |

|-----------------------|--|----------------|------------------|

| COLUMBUS, OHIO        |  | <b>16236</b>   | <b>V62/11611</b> |

|                       |  | REV            | PAGE 3           |

Stresses beyond those listed under "absolute maximum rating" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

<sup>2/</sup> Transient currents of up to 100 mA do not cause silicon controlled rectifier (SCR) latch up.

Use of this product beyond the manufacturers design rules or stated parameters is done at the user's risk. The manufacturer and/or distributor maintain no responsibility or liability for product used beyond the stated limits.

#### 2. APPLICABLE DOCUMENTS

JEDEC PUB 95 - Registered and Standard Outlines for Semiconductor Devices

(Applications for copies should be addressed to the JEDEC Office, 3103 North 10th Street, Suite 240-S, Arlington, VA 22201-2107 or online at http://www.jedec.org)

#### 3. REQUIREMENTS

- 3.1 <u>Marking</u>. Parts shall be permanently and legibly marked with the manufacturer's part number as shown in 6.3 herein and as follows:

- A. Manufacturer's name, CAGE code, or logo

- B. Pin 1 identifier

- C. ESDS identification (optional)

- 3.2 <u>Unit container</u>. The unit container shall be marked with the manufacturer's part number and with items A and C (if applicable) above.

- 3.3 <u>Electrical characteristics</u>. The maximum and recommended operating conditions and electrical performance characteristics are as specified in 1.3, 1.4, and table I herein.

- 3.4 Design, construction, and physical dimension. The design, construction, and physical dimensions are as specified herein.

- 3.5 Diagrams.

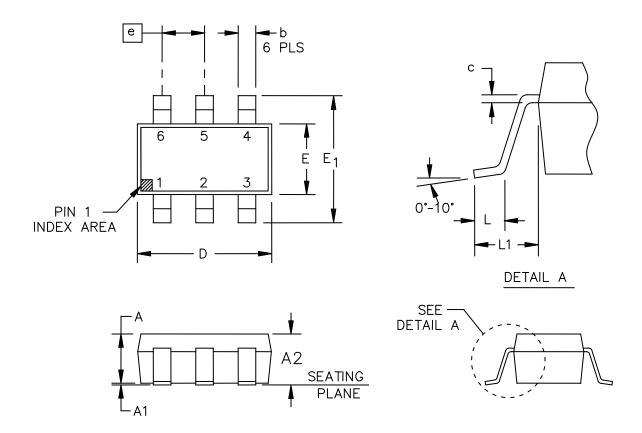

- 3.5.1 Case outline. The case outline shall be as shown in 1.2.2 and figure 1.

- 3.5.2 <u>Terminal connections</u>. The terminal connections shall be as shown in figure 2.

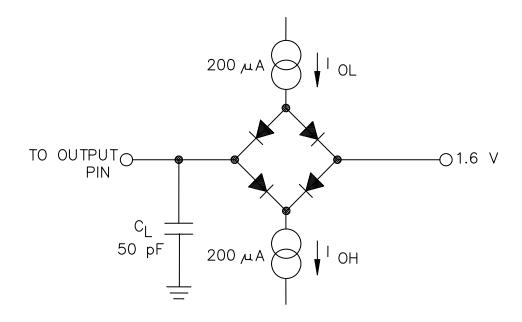

- 3.5.3 <u>Load circuit for digital output timing specifications</u>. The load circuit for digital output timing specifications shall be as shown in figure 3.

| DLA LAND AND MARITIME | SIZE     | CODE IDENT NO. | DWG NO.          |

|-----------------------|----------|----------------|------------------|

| COLUMBUS, OHIO        | <b>A</b> | <b>16236</b>   | <b>V62/11611</b> |

|                       |          | REV            | PAGE 4           |

TABLE I. Electrical performance characteristics. 1/

| Test                                                 | Symbol          | Conditions 2/                                | Temperature,    | Device<br>type | Lir                     | nits    | Unit |  |

|------------------------------------------------------|-----------------|----------------------------------------------|-----------------|----------------|-------------------------|---------|------|--|

|                                                      |                 |                                              | ^               |                | Min                     | Max     |      |  |

| Dynamic performance se                               | ection.         | f <sub>IN</sub> = 100 kHz sine wave          |                 |                |                         |         |      |  |

| Signal to (noise +                                   | SINAD           |                                              | +25°C           | 01             | 70                      |         | dB   |  |

| distortion)                                          |                 |                                              | -55°C to +125°C |                | 69                      |         |      |  |

| Signal to noise ratio                                | SNR             |                                              | -55°C to +125°C | 01             | 70                      |         | dB   |  |

| Total harmonic distortion                            | THD             |                                              | -55°C to +125°C | 01             | -78 typical             |         | dB   |  |

| Peak harmonic or spurious noise                      | SFDR            |                                              | -55°C to +125°C | 01             | -80 typical             |         | dB   |  |

| Intermodulation<br>distortion, second<br>order terms | IMD             | fa = 103.5 kHz, fb = 113.5 kHz               | -55°C to +125°C | 01             | -78 typical             |         | dB   |  |

| Intermodulation<br>distortion, third<br>order terms  | IMD             | fa = 103.5 kHz, fb = 113.5 kHz               | -55°C to +125°C | 01             | -78 typical             |         | dB   |  |

| Aperture delay                                       |                 |                                              | -55°C to +125°C | 01             | 10 typical              |         | ns   |  |

| Aperture jitter                                      |                 |                                              | -55°C to +125°C | 01             | 30 typical              |         | ps   |  |

| Full power bandwidth                                 | FPBW            | At 3 dB                                      | -55°C to +125°C | 01             | 6.5 typical             |         | MHz  |  |

| DC accuracy section.                                 | •               | V <sub>DD</sub> = 2.35 V to 3.6 V <u>3</u> / |                 |                |                         |         |      |  |

| Resolution                                           |                 |                                              | -55°C to +125°C | 01             | 12                      |         | Bits |  |

| Integral nonlinearity                                | INL             |                                              | +25°C           | 01             | ±0.6                    | typical | LSB  |  |

|                                                      |                 |                                              | -55°C to +125°C |                |                         | ±1.5    |      |  |

| Differential nonlinearity                            | DNL             | Guaranteed in missed codes to                | +25°C           | 01             | ±0.75                   | typical | LSB  |  |

|                                                      |                 | 12 bits                                      | -55°C to +125°C |                | -0.9                    | +1.5    |      |  |

| Offset error                                         | OE              |                                              | -55°C to +125°C | 01             |                         | ±2      | LSB  |  |

| Gain error                                           | GE              |                                              | -55°C to +125°C | 01             |                         | ±2      | LSB  |  |

| Analog input section.                                |                 |                                              |                 | •              |                         | •       | •    |  |

| Input voltage ranges                                 | VIN             |                                              | -55°C to +125°C | 01             | 0 to<br>V <sub>DD</sub> |         | V    |  |

| DC leakage current                                   |                 |                                              | -55°C to +125°C | 01             |                         | ±1      | μА   |  |

| Input capacitance                                    | C <sub>IN</sub> |                                              | -55°C to +125°C | 01             | 30 ty                   | /pical  | pF   |  |

| DLA LAND AND MARITIME | SIZE | CODE IDENT NO. | DWG NO.          |

|-----------------------|------|----------------|------------------|

| COLUMBUS, OHIO        | A    | <b>16236</b>   | <b>V62/11611</b> |

|                       |      | REV            | PAGE 5           |

TABLE I. Electrical performance characteristics - continued.  $\underline{\textbf{1}}/$

| Test                              | Symbol           | Conditions 2/                                                       | Temperature,    | Device<br>type | Lir                      | nits   | Unit |

|-----------------------------------|------------------|---------------------------------------------------------------------|-----------------|----------------|--------------------------|--------|------|

|                                   |                  |                                                                     |                 |                | Min                      | Max    |      |

| Logic input section.              |                  |                                                                     | •               |                |                          |        |      |

| Input high voltage                | VINH             |                                                                     | -55°C to +125°C | 01             | 2.4                      |        | V    |

|                                   |                  | V <sub>DD</sub> = 2.35 V                                            |                 |                | 1.8                      |        |      |

| Input low voltage                 | V <sub>INL</sub> | V <sub>DD</sub> = 3 V                                               | -55°C to +125°C | 01             |                          | 0.4    | V    |

|                                   |                  | V <sub>DD</sub> = 5 V                                               |                 |                |                          | 0.8    |      |

| Input current, SCLK pin           | I <sub>IN</sub>  | Typically 10 nA, V <sub>IN</sub> = 0 V or V <sub>DD</sub>           | -55°C to +125°C | 01             |                          | ±1     | μА   |

| Input current, CS pin             | I <sub>IN</sub>  |                                                                     | -55°C to +125°C | 01             | ±1 ty                    | /pical | μА   |

| Input capacitance                 | C <sub>IN</sub>  | <u>4</u> /                                                          | -55°C to +125°C | 01             |                          | 10     | pF   |

| Logic output section.             | ı                |                                                                     | 1               | I              | I                        |        | 1    |

| Output high voltage               | Voн              | I <sub>SOURCE</sub> = 200 μA,<br>V <sub>DD</sub> = 2.35 V to 5.25 V | -55°C to +125°C | 01             | V <sub>DD</sub><br>- 0.2 |        | V    |

| Output low voltage                | V <sub>OL</sub>  | I <sub>SINK</sub> = 200 μA                                          | -55°C to +125°C | 01             |                          | 0.4    | V    |

| Floating state leakage current    |                  |                                                                     | -55°C to +125°C | 01             |                          | ±10    | μА   |

| Floating state output capacitance |                  | 4/                                                                  | -55°C to +125°C | 01             |                          | 10     | pF   |

| Output coding                     |                  | Straight (natural) binary                                           | -55°C to +125°C | 01             |                          |        |      |

| Conversion rate section.          | ·                |                                                                     |                 |                | l                        |        |      |

| Conversion time                   |                  | 16 SCLK                                                             | -55°C to +125°C | 01             |                          | 1.33   | μS   |

| Track and hold                    |                  | Full scale step input                                               | -55°C to +125°C | 01             |                          | 500    | ns   |

| acquisition time                  |                  | Sine wave input ≤ 100 kHz                                           | 1               |                |                          | 400    | 1    |

| Throughput rate                   |                  |                                                                     | -55°C to +125°C | 01             |                          | 600    | kSPS |

| DLA LAND AND MARITIME |  | CODE IDENT NO. | DWG NO.          |

|-----------------------|--|----------------|------------------|

| COLUMBUS, OHIO        |  | <b>16236</b>   | <b>V62/11611</b> |

|                       |  | REV            | PAGE 6           |

TABLE I. Electrical performance characteristics - continued.  $\underline{1}/$

| Test                                               | Symbol          | Conditions <u>2</u> /                                                                                                 | Temperature,    | Device<br>type | Lir  | Unit  |    |  |

|----------------------------------------------------|-----------------|-----------------------------------------------------------------------------------------------------------------------|-----------------|----------------|------|-------|----|--|

|                                                    |                 |                                                                                                                       |                 |                | Min  | Max   |    |  |

| Power requirements sec                             | tion.           |                                                                                                                       | ·               |                |      |       |    |  |

| Supply voltage                                     | V <sub>DD</sub> |                                                                                                                       | -55°C to +125°C | 01             | 2.35 | 5.25  | V  |  |

| Supply current,<br>normal mode (static)            | I <sub>DD</sub> | Digital I/Ps = 0 V or $V_{DD}$ ,<br>$V_{DD}$ = 4.75 V to 5.25 V,<br>SCLK on or off                                    | -55°C to +125°C | 01             | 2 ty | pical | mA |  |

|                                                    |                 | Digital I/Ps = 0 V or $V_{DD}$ ,<br>$V_{DD}$ = 2.35 V to 3.6 V,<br>SCLK on or off                                     |                 |                | 1 ty |       |    |  |

| Supply current,<br>normal mode<br>(operational)    | I <sub>DD</sub> | Digital I/Ps = 0 V or $V_{DD}$ ,<br>$V_{DD}$ = 4.75 V to 5.25 V,<br>$f_{SAMPLE}$ = $f_{SAMPLE}$ max $\underline{5}$ / | -55°C to +125°C | 01             |      | 3     | mA |  |

|                                                    |                 | Digital I/Ps = 0 V or $V_{DD}$ ,<br>$V_{DD}$ = 2.35 V to 3.6 V,<br>$f_{SAMPLE}$ = $f_{SAMPLE}$ max $\underline{5}$ /  |                 |                |      | 1.4   |    |  |

| Full power down mode                               | FPDM            | SCLK off                                                                                                              | -55°C to +125°C | 01             |      | 1     | μА |  |

|                                                    |                 | SCLK on                                                                                                               |                 |                |      | 80    | 1  |  |

| Power dissipation,<br>normal mode<br>(operational) | PD              | V <sub>DD</sub> = 5 V,<br>f <sub>SAMPLE</sub> = f <sub>SAMPLE</sub> max <u>5</u> /                                    | -55°C to +125°C | 01             |      | 15    | mW |  |

|                                                    |                 | V <sub>DD</sub> = 3 V,<br>f <sub>SAMPLE</sub> = f <sub>SAMPLE</sub> max <u>5</u> /                                    |                 |                |      | 4.2   |    |  |

| Power dissipation, full power down                 | PD              | V <sub>DD</sub> = 5 V, SCLK off                                                                                       | -55°C to +125°C | 01             |      | 5     | μW |  |

|                                                    |                 | V <sub>DD</sub> = 3 V, SCLK off                                                                                       |                 |                |      | 3     |    |  |

| DLA LAND AND MARITIME | SIZE     | CODE IDENT NO. | DWG NO.          |

|-----------------------|----------|----------------|------------------|

| COLUMBUS, OHIO        | <b>A</b> | <b>16236</b>   | <b>V62/11611</b> |

|                       |          | REV            | PAGE 7           |

TABLE I. Electrical performance characteristics - continued.  $\underline{1}/$

| Test                                                                            | Symbol         | Conditions 6/7/ | Temperature,    | Device<br>type | Limits        |     | Unit |

|---------------------------------------------------------------------------------|----------------|-----------------|-----------------|----------------|---------------|-----|------|

|                                                                                 |                |                 |                 |                | Min           | Max |      |

| Timing specifications se                                                        | ction.         | •               | •               | •              |               |     | •    |

| Serial clock 8/<br>frequency                                                    | fSCLK          | At 3 V          | -55°C to +125°C | 01             | 10            |     | kHz  |

| nequency                                                                        |                | At 5 V          |                 |                | 10            |     |      |

|                                                                                 |                | At 3 V          |                 |                |               | 12  | MHz  |

|                                                                                 |                | At 5 V          |                 |                |               | 12  |      |

| Conversion time                                                                 | tCONVERT       | At 3 V          | -55°C to +125°C | 01             | 16 x<br>tsclk |     |      |

|                                                                                 |                | At 5 V          |                 |                | 16 x<br>tsclk |     |      |

| Minimum quite time required between bus relinquish and start of next conversion | tQUIET         | At 3 V          | -55°C to +125°C | 01             | 50            |     | ns   |

|                                                                                 |                | At 5 V          |                 |                | 50            |     |      |

| Minimum CS pulse                                                                | t <sub>1</sub> | At 3 V          | -55°C to +125°C | 01             | 10            |     | ns   |

| width                                                                           |                | At 5 V          |                 |                | 10            |     |      |

| CS to SCLK setup                                                                | t <sub>2</sub> | At 3 V          | -55°C to +125°C | 01             | 10            |     | ns   |

| time                                                                            |                | At 5 V          |                 |                | 10            |     |      |

| Delay from CS 9/                                                                | t <sub>3</sub> | At 3 V          | -55°C to +125°C | 01             |               | 20  | ns   |

| until SDATA three state disabled                                                |                | At 5 V          |                 |                |               | 20  |      |

| Data access time <u>9/</u> after SCLK falling                                   | t <sub>4</sub> | At 3 V          | -55°C to +125°C | 01             |               | 40  | ns   |

| edge, A version                                                                 |                | At 5 V          |                 |                |               | 20  |      |

| Data access time <u>9/</u> after SCLK falling                                   | t <sub>4</sub> | At 3 V          | -55°C to +125°C | 01             |               | 70  | ns   |

| edge, B version                                                                 |                | At 5 V          |                 |                |               | 20  |      |

| DLA LAND AND MARITIME | SIZE | CODE IDENT NO. | DWG NO.          |

|-----------------------|------|----------------|------------------|

| COLUMBUS, OHIO        | A    | <b>16236</b>   | <b>V62/11611</b> |

|                       |      | REV            | PAGE 8           |

TABLE I. Electrical performance characteristics - continued. 1/

| Test                                   | Symbol            | Symbol Conditions <u>6</u> / <u>7</u> / |                 | Device<br>type             | Limits                     |       | Unit |

|----------------------------------------|-------------------|-----------------------------------------|-----------------|----------------------------|----------------------------|-------|------|

|                                        |                   |                                         | T <sub>A</sub>  |                            | Min                        | Max   |      |

| Timing specifications sec              | ction - continued | l.                                      | ·               |                            |                            |       |      |

| SCLK low pulse width t <sub>5</sub>    | At 3 V            | -55°C to +125°C                         | 01              | 0.4 x<br>t <sub>SCLK</sub> |                            | ns    |      |

|                                        |                   | At 5 V                                  |                 |                            | 0.4 x<br>t <sub>SCLK</sub> |       |      |

| SCLK high pulse width t <sub>6</sub>   | At 3 V            | -55°C to +125°C                         | 01              | 0.4 x<br>t <sub>SCLK</sub> |                            | ns    |      |

|                                        |                   | At 5 V                                  |                 |                            | 0.4 x<br>t <sub>SCLK</sub> |       |      |

| SCLK to data valid                     | t <sub>7</sub>    | At 3 V                                  | -55°C to +125°C | 01                         | 10                         |       | ns   |

| noid time                              |                   | At 5 V                                  |                 |                            | 10                         |       |      |

| SCLK falling edge 10/<br>to SDATA high | t <sub>8</sub>    | At 3 V                                  | -55°C to +125°C | 01                         | 10                         | 25    | ns   |

| impedance                              |                   |                                         | 10              | 25                         |                            |       |      |

| Power up time from                     | tpower-up         | At 3 V                                  | -55°C to +125°C | 01                         | 1 typ                      | oical | μS   |

| full power down                        |                   | At 5 V                                  |                 |                            | 1 typ                      | oical |      |

- Testing and other quality control techniques are used to the extent deemed necessary to assure product performance over the specified temperature range. Product may not necessarily be tested across the full temperature range and all parameters may not necessarily be tested. In the absence of specific parametric testing, product performance is assured by characterization and/or design.

- $\underline{2}$ / Unless otherwise specified,  $V_{DD}$  = 2.35 V to 5.25 V,  $f_{SCLK}$  = 12 MHz, and  $f_{SAMPLE}$  = 600 kSPS

- 3/ Specifications apply as typical figures when  $V_{DD} = 5.25 \text{ V}$ .

- 4/ Guaranteed by characterization.

- 5/ f<sub>SAMPLE</sub> max = 600 kSPS.

- $\underline{6}'$  3 V specifications apply from V<sub>DD</sub> = 2.35 V to 3.6 V and 5 V specifications apply from V<sub>DD</sub> = 4.75 V to 5.25 V.

- $\overline{2}$ / Guaranteed by characterization. All input signals are specified with tr = tf = 5 ns ( 10% to 90% of V<sub>DD</sub> ) and timed from a voltage level of 1.6 V.

- 8/ Mark/space ratio for the SCLK input is 40/60 to 60/40.

- 9/ Measured with the load circuit of figure 3 and defined as the time required for the output to cross 0.8 V to 2.0 V.

- 10/ t8 is derived from the measured time taken by the data output to change 0.5 V when loaded with the circuit in figure 3. The measured number is then extrapolated to remove the effects of charging or discharging the 50 pF capacitor. This means that the time, t<sub>8</sub>, is the true bus relinquish time of the part and is independent of the bus loading.

| DLA LAND AND MARITIME | SIZE     | CODE IDENT NO. | DWG NO.          |

|-----------------------|----------|----------------|------------------|

| COLUMBUS, OHIO        | <b>A</b> | <b>16236</b>   | <b>V62/11611</b> |

|                       |          | REV            | PAGE 9           |

FIGURE 1. Case outline.

| DLA LAND AND MARITIME | SIZE | CODE IDENT NO. | DWG NO.          |

|-----------------------|------|----------------|------------------|

| COLUMBUS, OHIO        | A    | <b>16236</b>   | <b>V62/11611</b> |

|                       |      | REV            | PAGE 10          |

|        | Dimensions |       |             |      |             |  |

|--------|------------|-------|-------------|------|-------------|--|

| Symbol | Inches     |       | nbol Inches |      | Millimeters |  |

|        | Min        | Max   | Min         | Max  |             |  |

| А      | 0.035      | 0.051 | 0.90        | 1.30 |             |  |

| A1     | 0.001      | 0.005 | 0.05        | 0.15 |             |  |

| A2     | 0.037      | 0.057 | 0.95        | 1.45 |             |  |

| b      | 0.011      | 0.019 | 0.30        | 0.50 |             |  |

| С      | 0.003      | 0.007 | 0.08        | 0.20 |             |  |

| D      | 0.110      | 0.118 | 2.80        | 3.00 |             |  |

| Е      | 0.059      | 0.069 | 1.50        | 1.70 |             |  |

| E1     | 0.102      | 0.118 | 2.60        | 3.00 |             |  |

| е      | 0.037 BSC  |       | 0.95        | BSC  |             |  |

| L      | 0.013      | 0.021 | 0.35        | 0.55 |             |  |

| L1     | 0.023 BSC  |       | 0.60        | BSC  |             |  |

# NOTES:

- Controlling dimensions are millimeter, inch dimensions are given for reference only.

Falls within reference to JEDEC MO-178-AB.

FIGURE 1. Case outline - Continued.

| DLA LAND AND MARITIME | SIZE | CODE IDENT NO. | DWG NO.          |

|-----------------------|------|----------------|------------------|

| COLUMBUS, OHIO        | A    | <b>16236</b>   | <b>V62/11611</b> |

|                       |      | REV            | PAGE 11          |

| Device type     | 01              |                                                                                                                                                                                                                                                                                                        |  |

|-----------------|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Case outline    |                 | Х                                                                                                                                                                                                                                                                                                      |  |

| Terminal number | Terminal symbol | Description                                                                                                                                                                                                                                                                                            |  |

| 1               | V <sub>DD</sub> | Power supply input. The V <sub>DD</sub> range for the device is from 2.35 V to 5.25 V.                                                                                                                                                                                                                 |  |

| 2               | GND             | Analog ground. Ground reference point for all circuitry on the part. All analog input signals should be referred to this GND voltage.                                                                                                                                                                  |  |

| 3               | V <sub>IN</sub> | Analog input. Single ended analog input channel. The input range is 0 V to V <sub>DD</sub> .                                                                                                                                                                                                           |  |

| 4               | SCLK            | Serial clock. Logic input. SCLK provides the serial clock for accessing data from the part. This clock input is also used as the clock source for the device conversion process.                                                                                                                       |  |

| 5               | SDATA           | Data out. Logic output. The conversion result is provided on this output as serial data stream. The bits are clocked out on the falling edge of the SCLK input. The data stream from the device consists of four leading zeros followed by the 12 bits of conversion data; this is provided MSB first. |  |

| 6               | CS              | Chip select. Active low logic input. This input provides the dual function of initiating conversions on the device and framing the serial data transfer.                                                                                                                                               |  |

FIGURE 2. <u>Terminal connections</u>.

| DLA LAND AND MARITIME | SIZE | CODE IDENT NO. | DWG NO.          |

|-----------------------|------|----------------|------------------|

| COLUMBUS, OHIO        | A    | <b>16236</b>   | <b>V62/11611</b> |

|                       |      | REV            | PAGE 12          |

FIGURE 3. Load circuit for digital output timing specifications.

| DLA LAND AND MARITIME | SIZE     | CODE IDENT NO. | DWG NO.          |

|-----------------------|----------|----------------|------------------|

| COLUMBUS, OHIO        | <b>A</b> | <b>16236</b>   | <b>V62/11611</b> |

|                       |          | REV            | PAGE 13          |

#### 4. VERIFICATION

4.1 <u>Product assurance requirements</u>. The manufacturer is responsible for performing all inspection and test requirements as indicated in their internal documentation. Such procedures should include proper handling of electrostatic sensitive devices, classification, packaging, and labeling of moisture sensitive devices, as applicable.

### 5. PREPARATION FOR DELIVERY

- 5.1 <u>Packaging</u>. Preservation, packaging, labeling, and marking shall be in accordance with the manufacturer's standard commercial practices for electrostatic discharge sensitive devices.

- 6. NOTES

- 6.1 ESDS. Devices are electrostatic discharge sensitive and are classified as ESDS class 1 minimum.

- 6.2 <u>Configuration control</u>. The data contained herein is based on the salient characteristics of the device manufacturer's data book. The device manufacturer reserves the right to make changes without notice. This drawing will be modified as changes are provided.

- 6.3 <u>Suggested source(s) of supply</u>. Identification of the suggested source(s) of supply herein is not to be construed as a guarantee of present or continued availability as a source of supply for the item.

| Vendor item drawing administrative control number 1/ | Device<br>manufacturer<br>CAGE code | Linearity error (LSB) 2/ | Vendor part number |

|------------------------------------------------------|-------------------------------------|--------------------------|--------------------|

| V62/11611-01XE                                       | 24355                               | ±1.5 maximum             | AD7476SRTZ-EP-RL7  |

- 1/ The vendor item drawing establishes an administrative control number for identifying the item on the engineering documentation.

- 2/ Linearity error refers to integral linearity error.

<u>CAGE code</u> <u>Source of supply</u>

24355 Analog Devices Route 1 Industrial Park

P.O. Box 9106 Norwood, MA 02062

Point of contact: Raheen Business Park Limerick, Ireland

| DLA LAND AND MARITIME | SIZE | CODE IDENT NO. | DWG NO.          |

|-----------------------|------|----------------|------------------|

| COLUMBUS, OHIO        | A    | <b>16236</b>   | <b>V62/11611</b> |

|                       |      | REV            | PAGE 14          |